|

| Home | Program | Committee | Application |

|

|

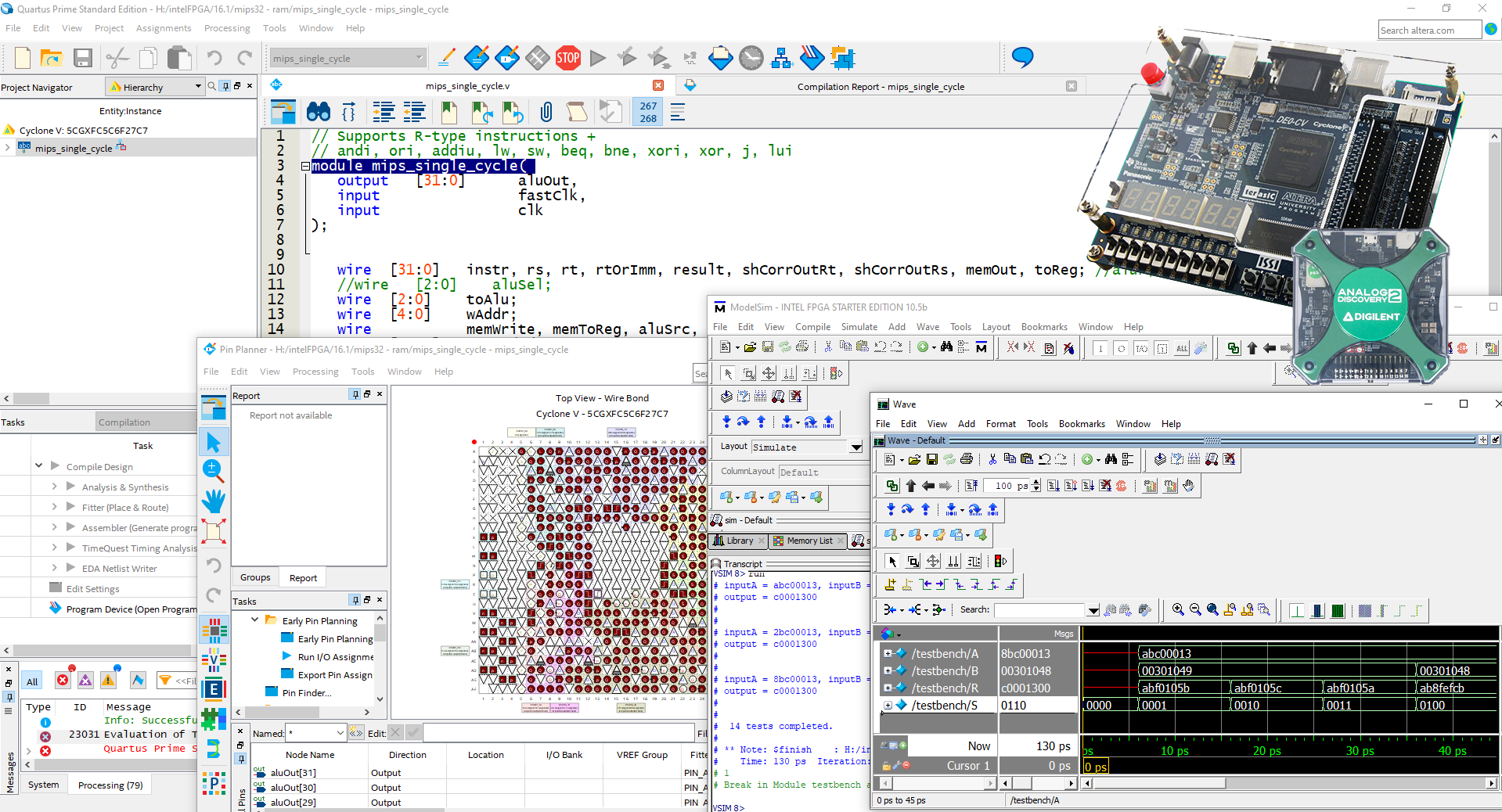

In this summer school, we start with a digital primer explaining the digital circuit design from scratch and finish with a case study including all steps from a C function to FPGA implementation for a computer algebra problem. Each day is composed of theoretical lectures (CX.X) and the experimental application of what has been learned (LX.X). During lab hours, the example designs are not only realized and simulated but also uploaded to actual FPGAs for further testing. Verilog HDL is taught throughout the lectures, including the structural, the dataflow and the behavioral Verilog. FSM construction and Verilog design of FSM machines are explained. For simulation, the testbench generation using Verilog is explained in detail. Reading inputs, writing outputs, displaying signals and different aspects of testbench writing are studied. Both Intel Quartus II and Modelsim tools are explained from installation to detailed circuit design, simulation, pin planning and FPGA upload.

Bu yaz okulu 8-12 Ağustos tarihlerinde Gebze Teknik Üniversitesi Bilgisayar Mühendisliği Bölümünde yapılacaktır.

|

|

|

|

|