|

GTU Integrated Circuits Lab |

|

| About ICL | Research | People | News | Contact |

|

|

Hardware Trojan Detection Based on SCA

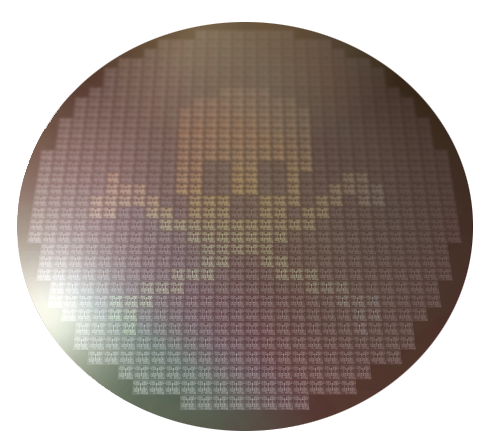

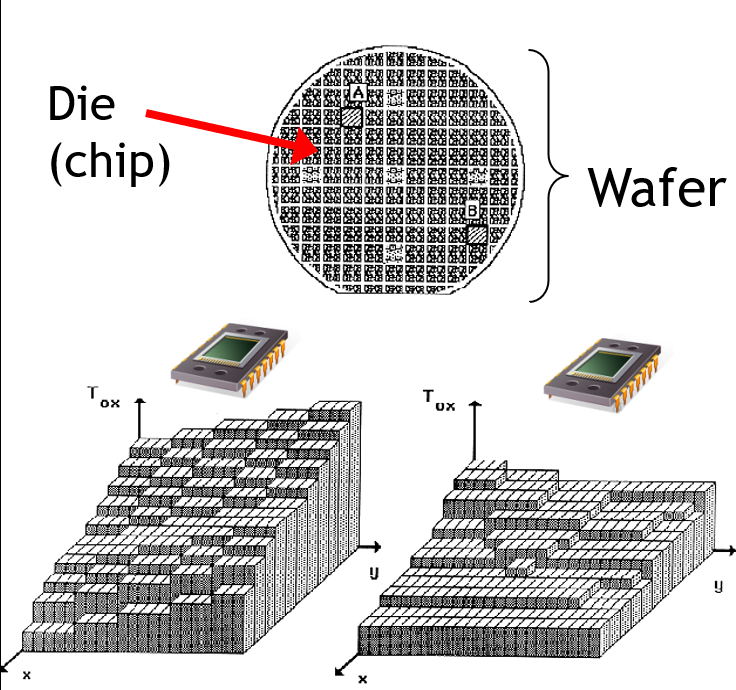

Hardware Trojan detection is a crucial problem with many dimensions and high complexity. No single method can satisfy security as hardware attacks have a great diversity. Destructive methods can only be sure about the irreversibly processed chips while the remaining ones are still untrusted. On the other hand, side channel analysis (SCA) based methods deeply suffer from inter and intra die variations, the inability to detect small Trojans as well as the requirement for golden chips. In this research, we utilize spatial correlations to get rid of the parameter variations effect, which hides the existence of hardware Trojan horse. Both delay and power of the circuit are used as side channel signals to detect Trojan existence in the circuit.

Delay Based Hardware Trojan Detection Exploiting Spatial Correlations to Suppress Variations (ELSEVIER-INTEGRATION)

FPGA Based Verification for the Difficulty of Delay Based Hardware Trojan Detection (ELECO2023) Hardware Trojan Detection Based on Correlated Path Delays in Defiance of Variations with Spatial Correlations (DATE2017) Acceleration of Spatial Correlation Based Hardware Trojan Detection Using Shared Grids Ratio (MACIS2019) Quantification of Power Based Hardware Trojan Detection Under Realistic Variations and Separation of Power Supplies (ELECO2019) |

|

Hardware Acceleration of Symbolic Computation

Computationally complex algorithms used in numerical methods or symbolic computation can be accelerated using by means of hardware and FPGAs. The hardware accelerated methods are then compared with the software equivalents to get the performance benefit of the implementation. The hardware implementation can be improved by more parallelism or independence to use any size of arithmetic units. The accelaration is currently being applied to Fundamental Parallelepiped Enumeration problem and Newton-Raphson numerical method. |

|

Register Allocation with Weighted Graph Coloring

Register allocation is important in compiler design to enhance the execution time of programs, as CPU registers operate significantly faster than memory locations. The challenge of optimally assigning program variables to a limited number of CPU registers requires innovative solutions within constrained timeframes, particularly when traditional methods are not applicable due to computational infeasibility on current CPU architectures. This study introduces BitVertex Evolutionary Algorithm (BitEA), a novel approach grounded in bitwise operations and bit-based solutions, designed to accelerate computational performance in register allocation. Our experimental results show that BitEA outperforms the existing methods by a factor of up to 60 across all tested scenarios in the DIMACS benchmarks. Furthermore, in terms of solution quality, BitEA achieves lower chromatic numbers on 9 DIMACS benchmarks compared to its closest contemporaries. This research underscores that BitEA has potential to set a new standard for register allocation through its superior speed and solution quality. |

|

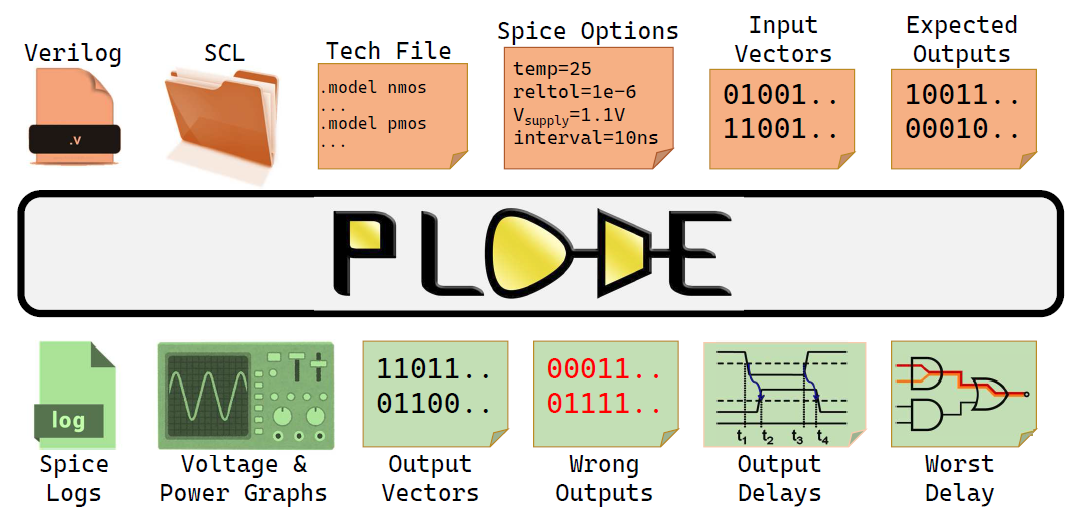

PLODE: Precise LOgic and DElay Simulator

Spice simulator is famous with its precision and preferred as a final stage verification tool. However, it needs a different circuit description than Verilog, and also its direct results are not meaningful in terms of speed and accuracy without further analysis. Commercial tools are proprietary and using them for conversion to Spice deck and analysis of the Spice results is costly in terms of both finance and effort. Precise Logic and Delay (PLODE) is a novel, research oriented, open source tool that can convert structural Verilog to Spice deck, perform simulations at the desired process technology node, analyze and visualize the results in terms of delay and functional accuracy. In order to help path delay based research, it can also extract a path from the circuit and simulate it without the need for a sensitizing input pair. The tool will be improved further to be able to perform static timing analysis and ATPG generation for path sensitization. It will be able to apply an accurate variation model both considering the inter and intra die variations. |

|

Statistical Timing Analysis

Static-timing analysis (STA) has been one of the most pervasive and successful analysis engines in the design of digital circuits for the last 20 years. However, in recent years, the increased loss of predictability in semiconductor devices has raised concern over the ability of STA to effectively model statistical variations. As a result, extensive research has been conducted on a statistical timing analysis of digital integrated circuits in the existence of statistical parameter variations. However, the proposed methods either lack accuracy or efficiency, which avoids coming up with an industry standard tool. Despite this fact, there is a certain consensus that Monte Carlo (MC) methods are accurate, so that they are called golden. In this research, novel techniques to combine different variance reduction methods in order to come up with a new timing yield estimator as accurate as SPICE-based standard MC (STD-MC) but much faster.

Accelerated Accurate Timing Yield Estimation Based on Control Variates and Importance Sampling (IEEE-TVLSI)

Stochastic Logical Effort as a Variation Aware Delay Model to Estimate Timing Yield (ELSEVIER-INTEGRATION) On the Accuracy of Monte Carlo Yield Estimators (VLSI-SOC2013) Fast Monte Carlo Estimation of Timing Yield WithImportance Sampling and Transistor-LevelCircuit Simulation (IEEE-TCAD) |

|

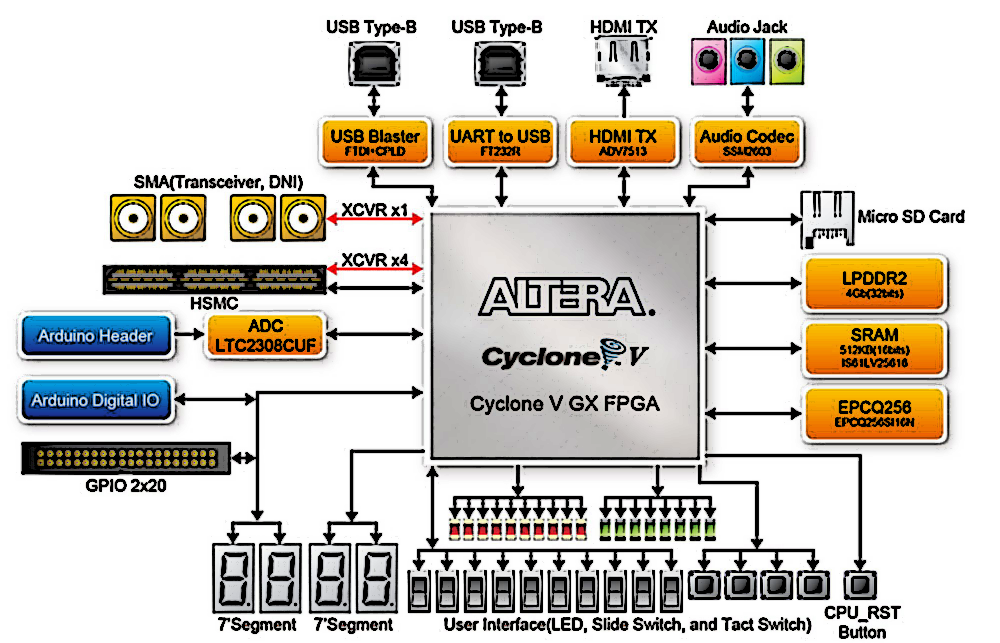

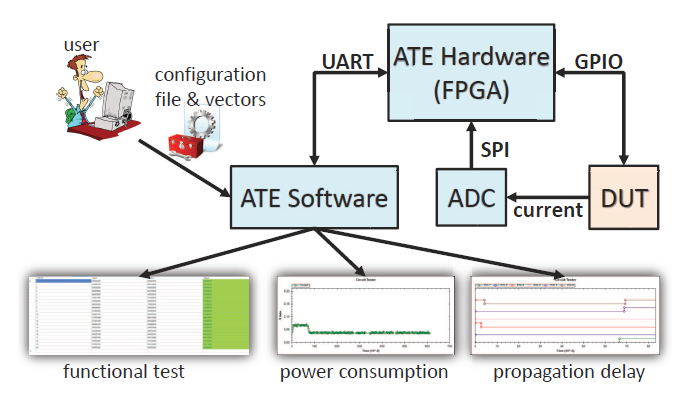

ELATE: Embedded Low Cost Automatic Test Equipment

Testing of digital circuits is a crucial problem. There are two types of Automatic Test Equipment (ATE): Very precise but complex and expensive test equipments called high-end ATE and their approximate but cheap alternatives called low-end ATE. In this paper we propose a very cheap, FPGA based embedded low-cost ATE (ELATE) that is capable of functional, speed/delay and power consumption tests. It is composed of FPGA hardware with six FSM modules written in Verilog and a computer software (user interface) communicating with the FPGA through UART. It can handle different I/O combinations and can detect delay with 4ns precision. It can both visually show the resultant voltage/current-time graphs and store them as text files. |

|

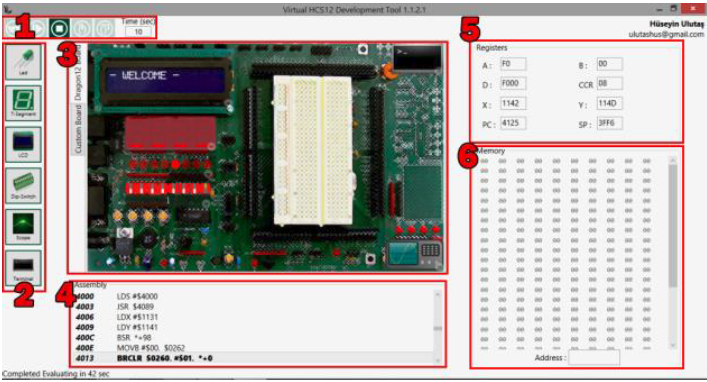

HCS12 EmumiS: Virtual HCS12 Development Tool

For learning and development purpose, microcontroller evaluation boards are widely used. However, the difficulty to get HCS12 boards domestically and also the expensiveness of them make it impossible to get for most of the students and hobbyists although HCS12 is very popular in education. In this research, we develop HCS12 EmumiS, which is a computer software that can not only simulate HCS12 instructions, memory and debug the program but also can fully emulate a customizable evaluation board, having components like LEDs, LCDs, 7-segment LEDs, buzzers and dip switches. |

|